## 【19】中華民國

## 【12】專利公報 (B)

【11】證書號數:I815646

【45】公告日: 中華民國 112 (2023) 年 09 月 11 日

[51] Int. Cl.: H01L21/28 (2006.01) H01L21/334 (2006.01)

H01L29/40 (2006.01) H01L29/76 (2006.01)

發明 全 25 頁

【54】名 稱:半導體元件及其製造方法

【21】申請案號:111133961 【22】申請日:中華民國 111 (2022) 年 09 月 07 日

【72】發明人: 徐閺正 (TW) HSU, WEN-CHENG;洪瑜亨 (TW) HONG, YU-HENG;黃耀

緯 (TW) HUANG, YAO-WEI; 洪國彬 (TW) HONG, KUO-BIN; 郭浩中 (TW)

KUO, HAO-CHUNG

【71】申 請 人: 鴻海精密工業股份有限公司 HON HAI PRECISION INDUSTRY CO.,

LTD.

新北市土城區中山路 66 號

國立陽明交通大學 NATIONAL YANG MING CHIAO TUNG

**UNIVERSITY**

新竹市大學路 1001 號

【74】代理人: 李世章;秦建譜

【56】參考文獻:

TW M627209 TW 202230831A

審查人員:于若天

## 【57】申請專利範圍

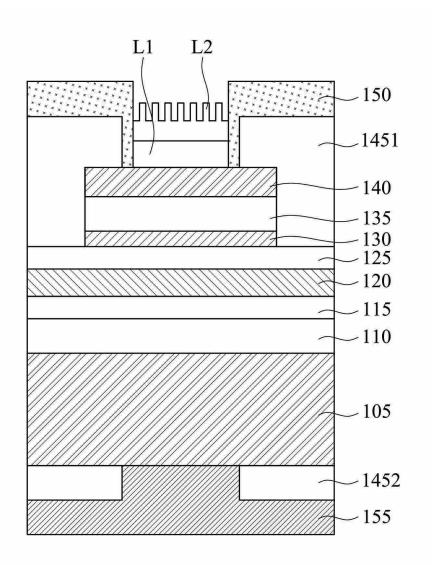

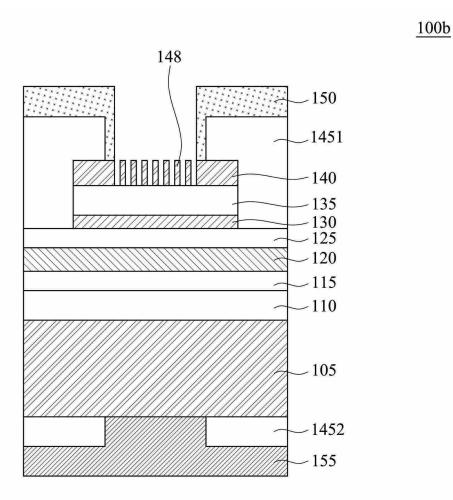

- 1. 一種半導體元件,包含:一第一接觸層,具有彼此相對的一第一表面與一第二表面,其中該第二表面上具有複數個微結構;一第二接觸層,位於該第一接觸層的該第一表面下方;一主動層,位於該第一接觸層與該第二接觸層之間;一光子晶體層,位於該主動層與該第二接觸層之間;一鈍化層,位於該第二接觸層上;一第一電極,位於該鈍化層上,且電性連接該第一接觸層的該第一表面;一第二電極,位於該鈍化層上,且電性連接該第二接觸層;一第一包覆層,位於該第一接觸層與該主動層之間;一第二包覆層,位於該第二接觸層與該光子晶體層之間,其中該第一接觸層、該第一包覆層、該主動層、該光子晶體層、該第二包覆層以及該第二接觸層為同質材料。

- 2. 如請求項1所述之半導體元件,其中該第一接觸層為n型接觸層與p型接觸層之其中一者,而該第二接觸層為n型接觸層與p型接觸層之其中另外一者。

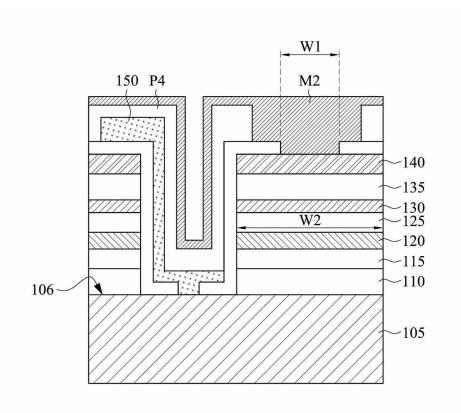

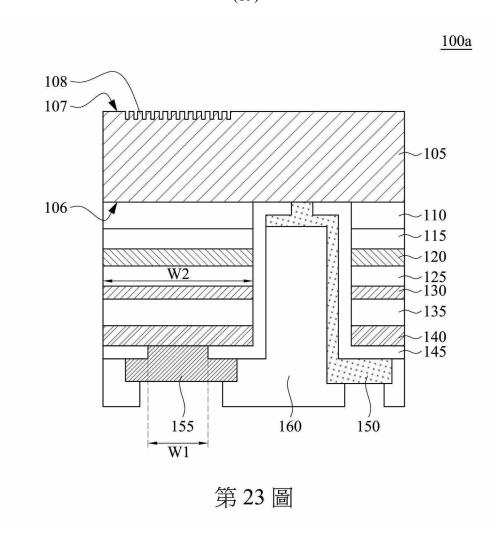

- 3. 如請求項1所述之半導體元件,其中該第二電極接觸該第二接觸層,且該第二電極與該 第二接觸層接觸的寬度小於該光子晶體層的寬度。

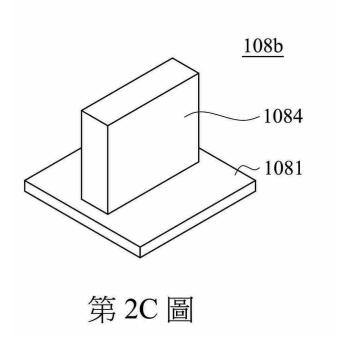

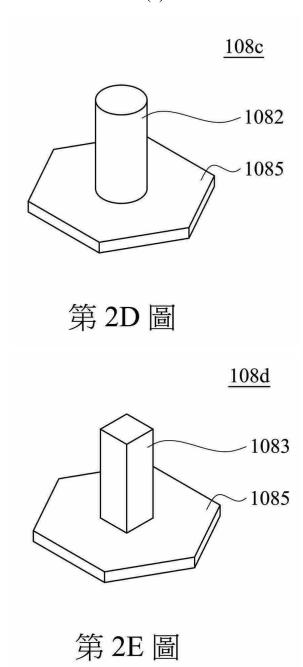

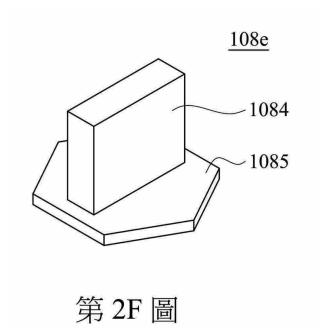

- 4. 如請求項1所述之半導體元件,其中每一該些微結構具有一底部與一凸部,其中該凸部 設置於該底部上,且該凸部投影在該底部的面積小於該底部的面積。

- 5. 如請求項 4 所述之半導體元件,其中該些底部為正方形或六角形,且該些凸部為圓形、 正方形、長方形或上述之組合。

- 6. 一種半導體元件的製造方法,包含:在一第一接觸層的一第一表面上依序形成一第一包覆層、一第一引導層、一主動層、一第二引導層、一光子晶體層、一第二包覆層以及一第二接觸層;在該第一包覆層、該第一引導層、該主動層、該第二引導層、該光子晶體層、該第二包覆層以及該第二接觸層中形成一溝槽;在該溝槽中與該第二接觸層上形成具有一第一開口與一第二開口的一鈍化層,其中該第一接觸層從該第一開口中裸露,該

第二接觸層從該第二開口中裸露;在該第一開口中與該鈍化層上形成一第一電極,使得該第一電極電性連接該第一開口中的該第一接觸層;在該第二開口中與該鈍化層上形成一第二電極,使得該第二電極電性連接該第二開口中的該第二接觸層;以及在該第一接觸層相對於該第一表面的一第二表面上形成複數個微結構。

- 7. 如請求項6所述之方法,其中在該第二表面上形成該些微結構更包含:在該第一接觸層的該第二表面上設置一硬遮罩層;在該硬遮罩層上形成圖案化的一電子阻擋層,其中該電子阻擋層具有複數個圖案;根據該電子阻擋層的該些圖案蝕刻該硬遮罩層與該第一接觸層,以形成該些微結構;以及去除該硬遮罩層與該電子阻擋層。

- 8. 如請求項 6 所述之方法,更包含:在形成該第二電極之後,在該鈍化層、該第一電極以及該第二電極上塗佈一保護層;平坦化該保護層;以及蝕刻位於該第一電極與該第二電極上的該保護層,使得該第一電極與該第二電極從該保護層中裸露。

- 9. 如請求項6所述之方法,其中在該第二開口中與該鈍化層上形成該第二電極更包含:在該第一電極與該鈍化層上形成一光阻層,其中該鈍化層的該第二開口從該光阻層中裸露;在該第二開口中與該光阻層上形成一金屬層;圖案化該金屬層,以形成該第二電極:以及去除該光阻層。

- 10. 如請求項 9 所述之方法,其中在該第二開口中與該光阻層上形成該金屬層,使得該金屬層在該第二開口中的寬度小於該光子晶體層的寬度。

## 圖式簡單說明

當結合隨附諸圖閱讀時,得自以下詳細描述最佳地理解本揭露之一實施方式。應強調,根據工業上之標準實務,各種特徵並未按比例繪製且僅用於說明目的。事實上,為了論述清楚,可任意地增大或減小各種特徵之尺寸。

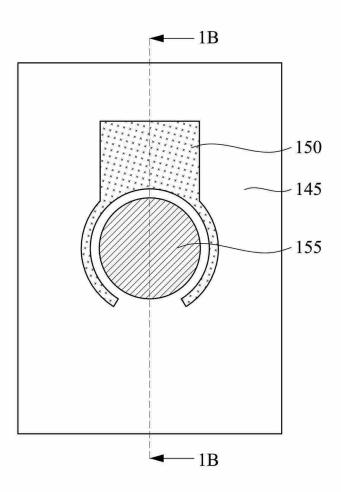

- 第 1A 圖繪示根據本揭露一實施方式之半導體元件的下視圖。

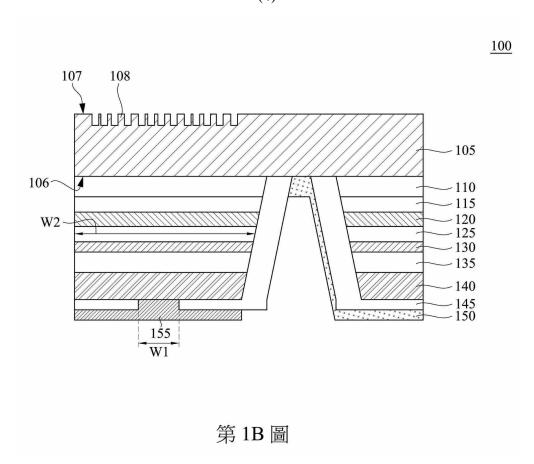

- 第 1B 圖繪示第 1A 圖的半導體元件沿線段 1B-1B 的剖面圖。

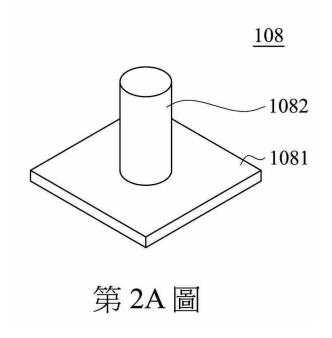

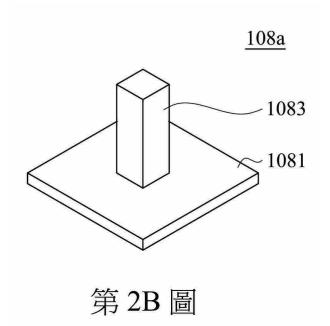

- 第 2A 圖至第 2F 圖繪示根據本揭露一些實施方式之微結構的立體圖。

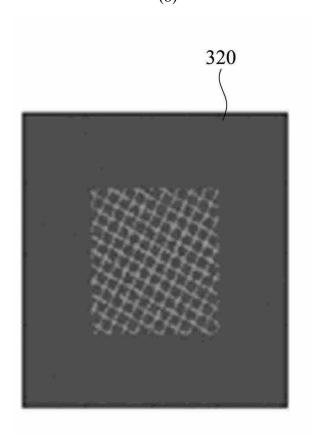

- 第 3A 圖與第 3B 圖繪示根據本揭露一些實施方式之光斑圖形的示意圖。

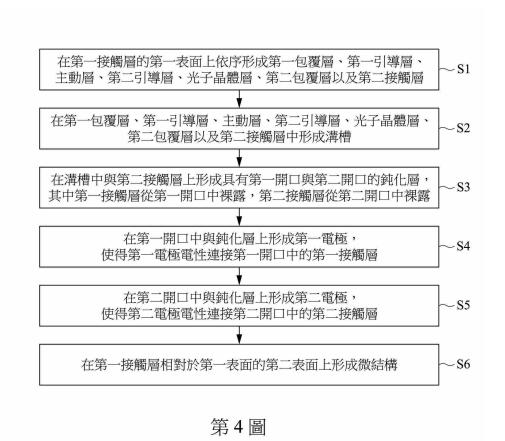

- 第 4 圖繪示根據本揭露一實施方式之半導體元件的製造方法的流程圖。

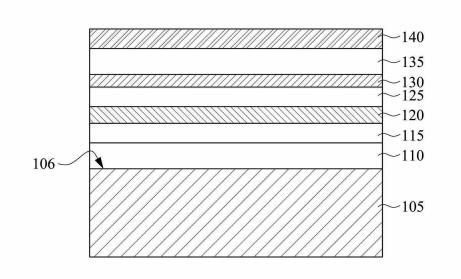

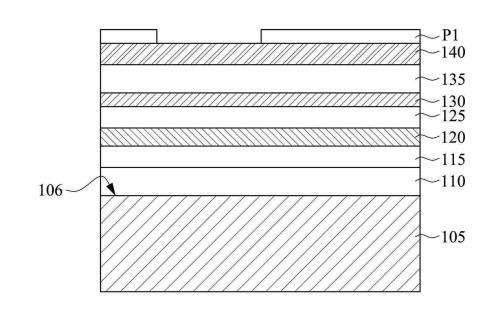

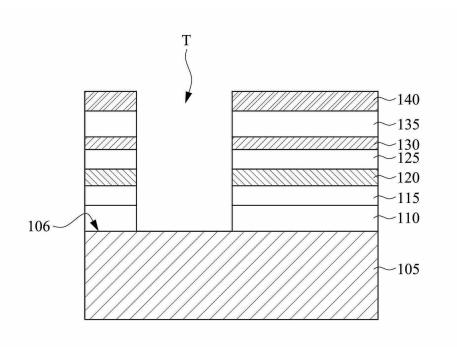

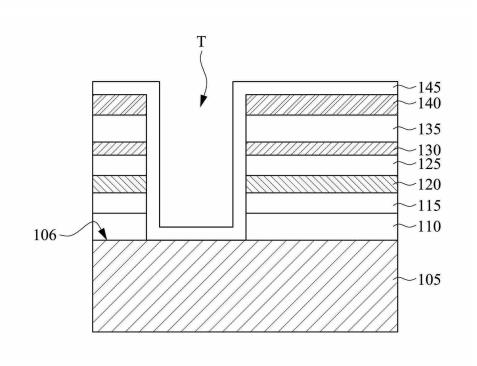

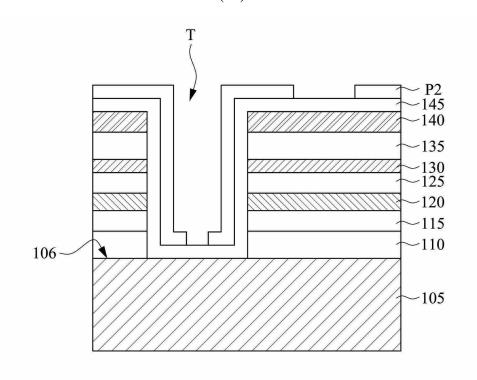

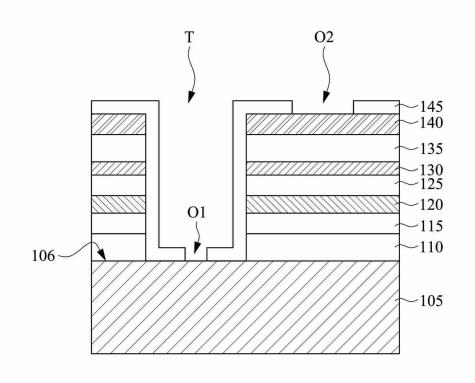

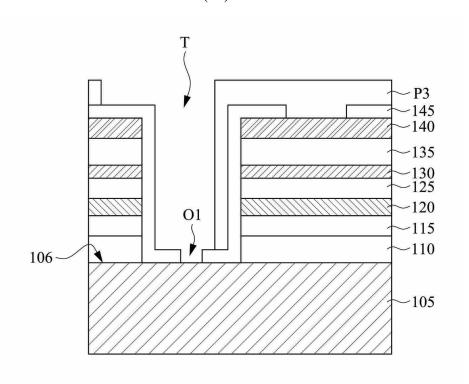

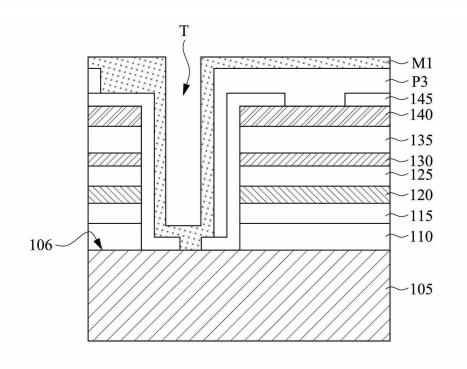

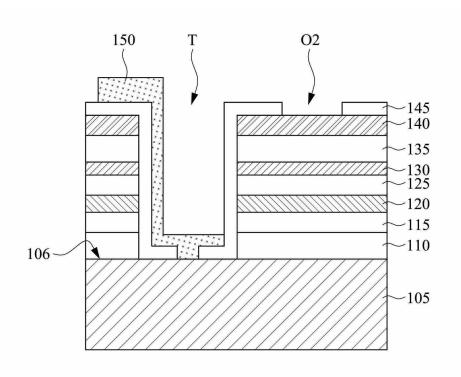

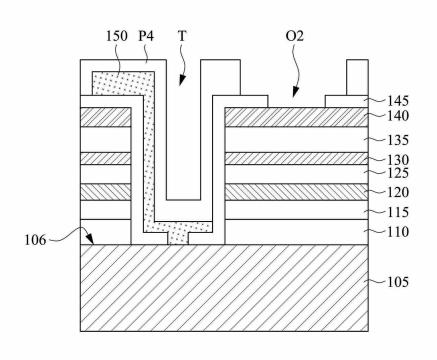

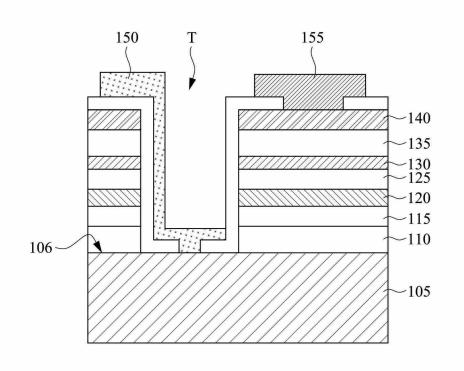

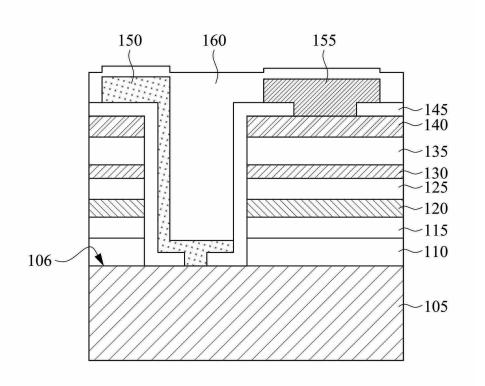

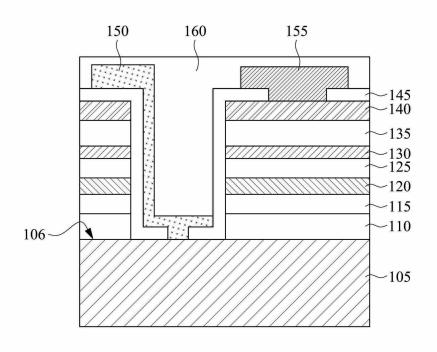

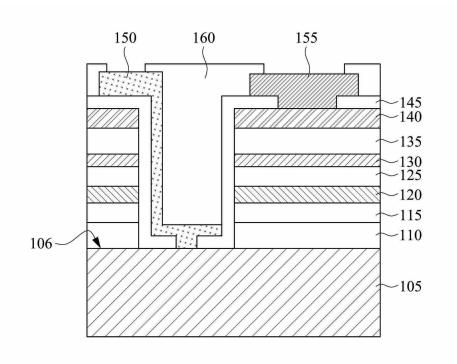

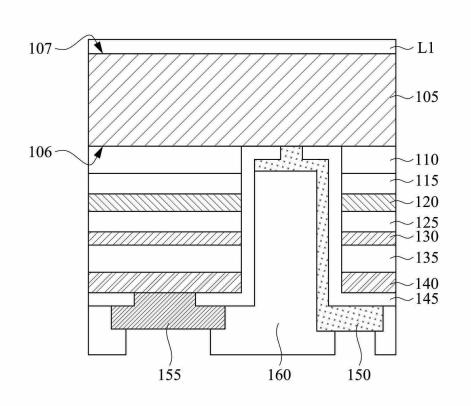

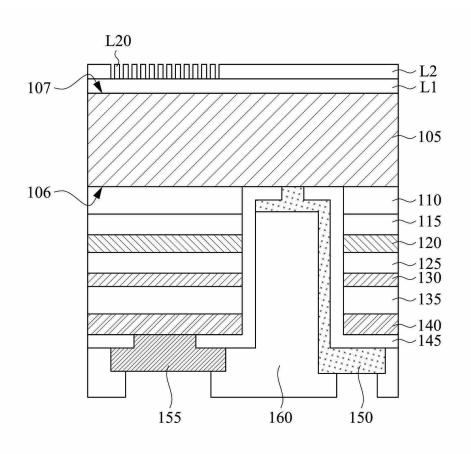

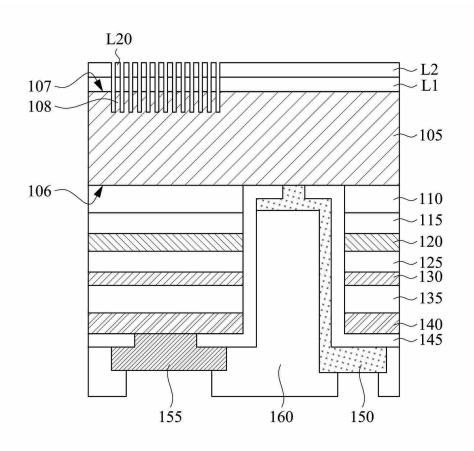

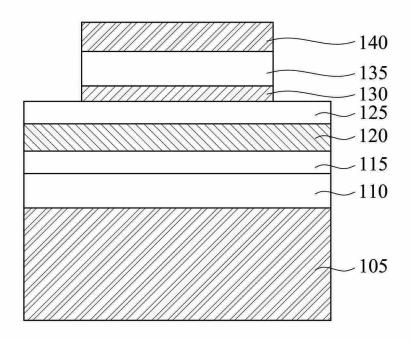

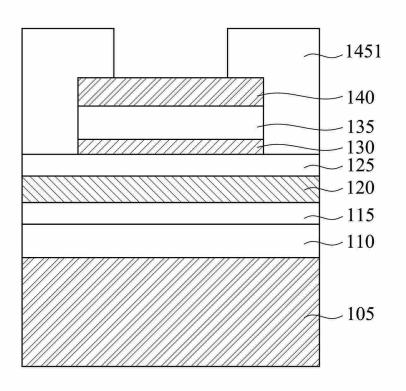

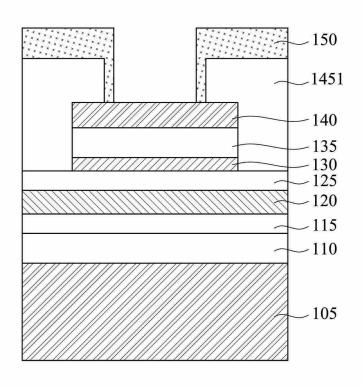

- 第 5 圖至第 23 圖繪示根據本揭露另一實施方式之半導體元件的製造方法在不同階段的剖面 圖。

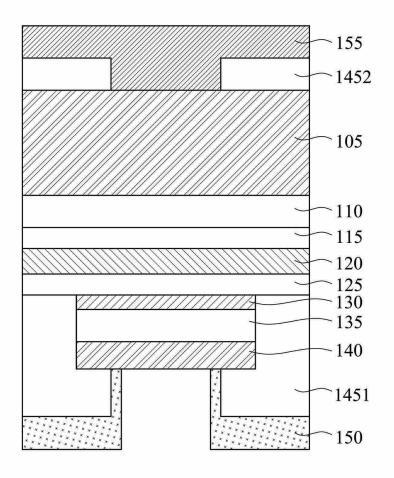

- 第 24 圖至第 29 圖繪示根據本揭露又一實施方式之半導體元件的製造方法在不同階段的剖面 圖。

<u>100</u>

第 1A 圖

第 3A 圖

第 3B 圖

- 10673 -

第5圖

第6圖

第7圖

第8圖

第9圖

第10圖

第11圖

第12圖

第13圖

第14圖

第15圖

第16圖

第17圖

第18圖

第19圖

第20圖

第21圖

第22圖

第24圖

第25圖

第26圖

第27圖

第28圖

第29圖